Google Summer of Code 2024

Transforming the OpenHW High Performance Data Cache into a High Performance Instruction Cache

Mentor: Jonathan Balkind, César Fuguet Tortolero, Noelia Oliete Escuín

Organization: Free and Open Source Silicon Foundation

Project Page: here!

Synopsis

As computing technology advances, the need for flexible and high-performance cache solutions is growing. The importance of cache designs that meet different needs is increasing, and new frameworks are being developed.

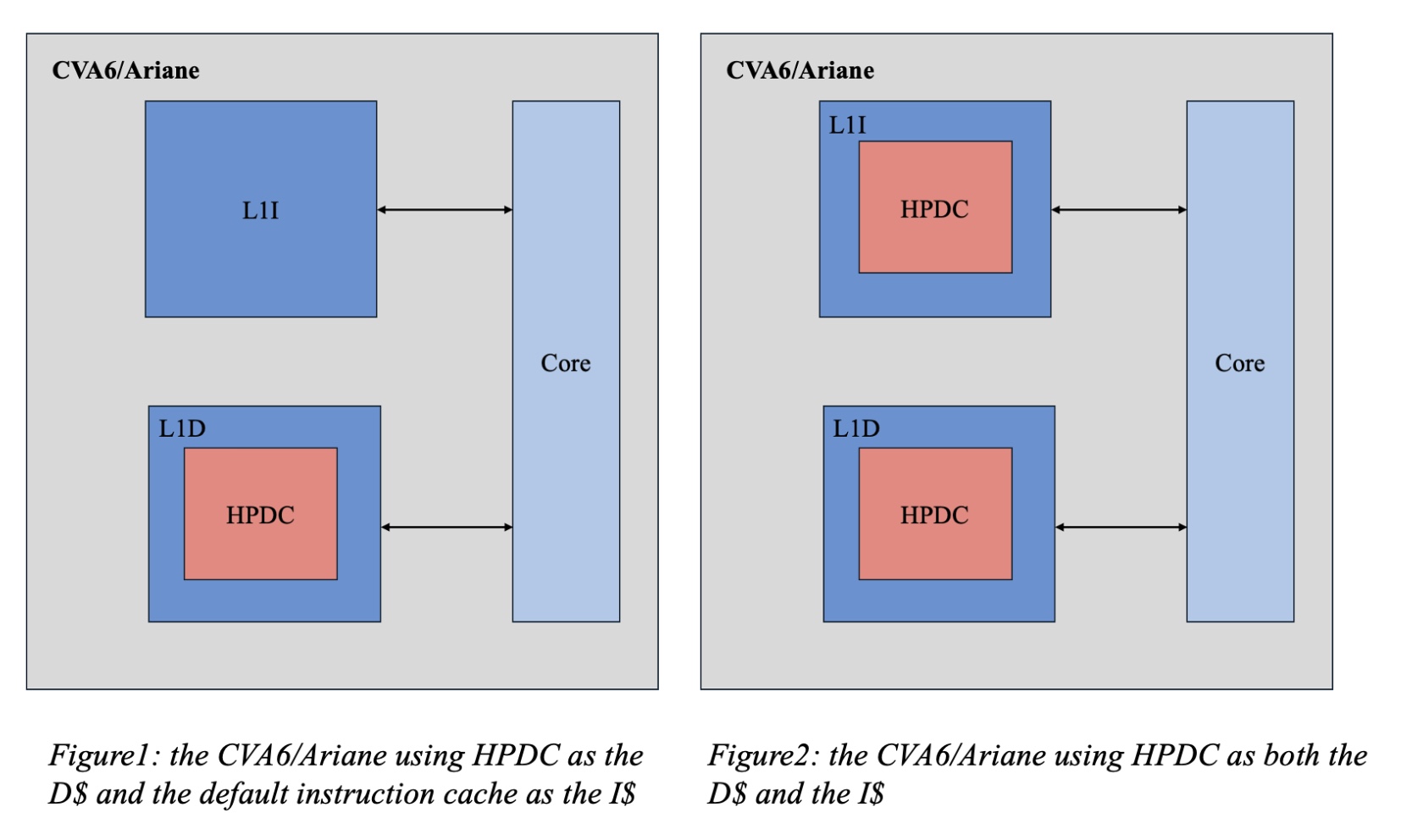

The CVA6/Ariane is an open-source RISC-V processor, and there is active growth in its ecosystem and its surrounding technologies, in addition to the development of the core itself. The CVA6/Ariane core supports several different L1 data caches for different contexts and user demands, and HPDC is currently an available high performance data cache for the CVA6/Ariane.

HPDC is an open-source, Out-of-Order L1 data cache that supports multi-request and multi-issue, capable of handling multiple requests and cache misses concurrently.

In this project, we focus on extending the HPDC to make it usable as an instruction cache.

Project Idea

The main goal of this project can be summarized in Figures 1 and 2. Figure 1 shows the CVA6/Ariane design using HPDC as a data cache and the default instruction cache as the instruction cache. In contrast, Figure 2 shows HPDC being used as both the data cache and the instruction cache.

Progress Report

-

creating the HPDC wrapper 【completed】 PR#2173

We created an hpdcache wrapper module that includes a prefetcher wrapper and an interface adapter with CVA6/Ariane in addition to hpdcache, the main and top module of HPDC. We decided to aim to make this hpdcache wrapper module usable as both an instruction cache and a data cache by instantiating it.

-

making the hpdcache wrapper to function as an instruction cache 【ongoing】 PR#2288, PR#2269

In this PR, the main focus is on developing/modifying and debugging the adapter that interfaces with the core and the AXI arbiter that interfaces with memory, when using HPDC as an instruction cache.

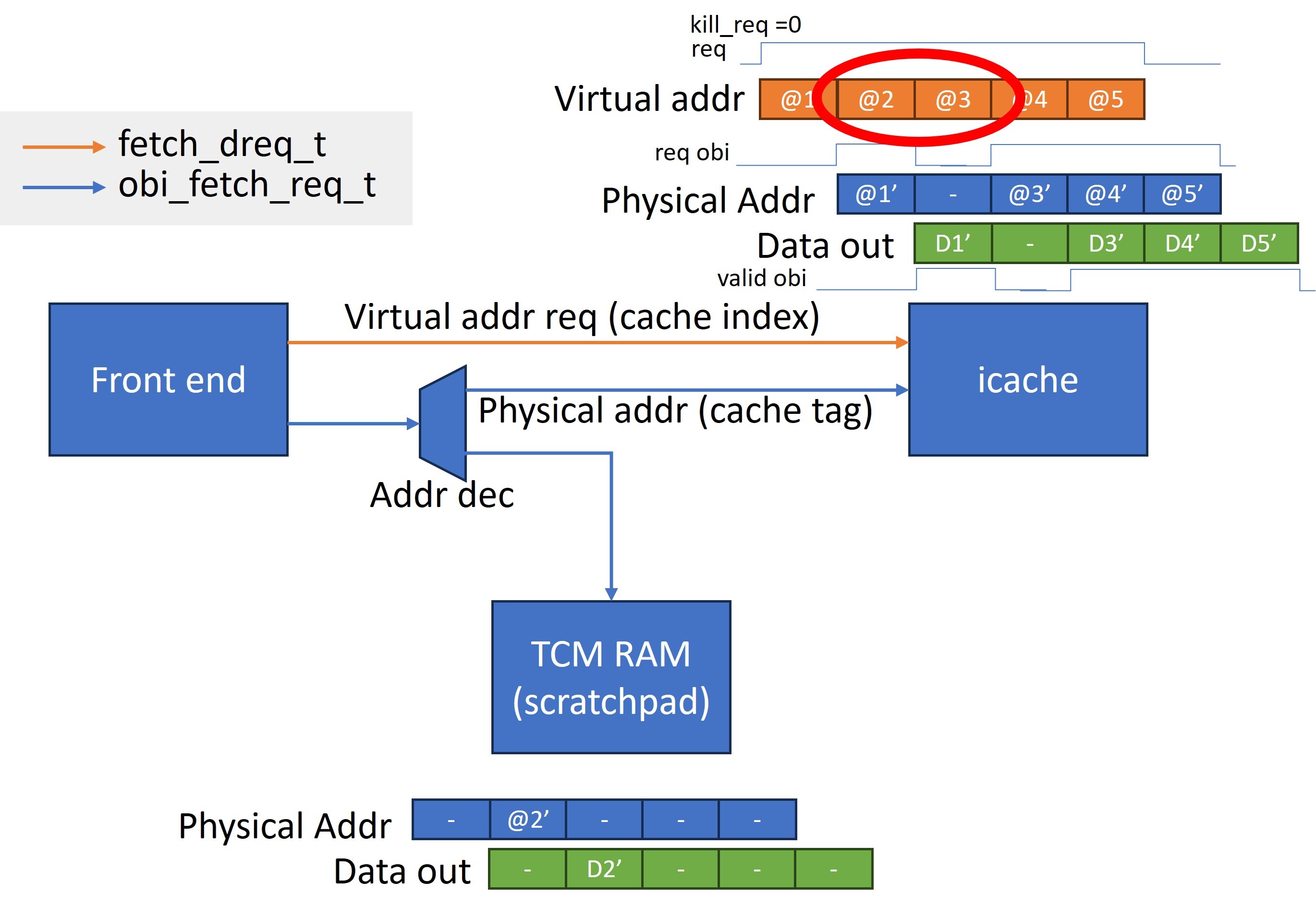

The key feature of the adapter is that it has been designed to support the OBI interface. The OBI interface is a bus interface that is being newly introduced in the CVA6/Ariane. It is assumed that a scratchpad, which does not benefit from the cache, is also used. Therefore there are cases where the physical address is not transmitted to the cache (instead, it is transmitted to the scratchpad). HPDC does not support this case, so we implemented a feature in the adapter that issues a kill request to HPDC when the corresponding physical address is not transmitted. (cf. Figure3)

With respect to the AXI arbiter, we modified it to split the ports that handle requests for misses and non-cacheable requests. The previous instruction cache uses a single port since it handles a single request, but we made this change to take advantage of HPDC’s ability to handle multiple requests.

Currently, this PR has not yet passed the RISC-V tests and is still being debugged. After passing the tests, I plan to add a feature that makes it configurable to switch between the original instruction cache and the instruction cache using HPDC. Then, I will split the PR into separate parts for easier review and aim to merge them. (PR#2269 is a partial implementation of the adapter.)

and its actual waveform (below)

Ongoing development

The following are the tasks I will continue working on:

- continuing debugging until the riscv tests pass

- adding a feature that makes it configurable to switch between the original instruction cache and the instruction cache using HPDC

- Creating PRs for each part and submit them for review

- Validating modifications in synthesis (ASIC and FPGA)